STM32——GPIO(三)

一、GPIO简介

•GPIO(General Purpose Input Output)通用输入输出口

•可配置为8种输入输出模式

•引脚电平:0V~3.3V,部分引脚可容忍5V

•输出模式下可控制端口输出高低电平,用以驱动LED、控制蜂鸣器、模拟通信协议输出时序等

•输入模式下可读取端口的高低电平或电压,用于读取按键输入、外接模块电平信号输入、ADC电压采集、模拟通信协议接收数据等

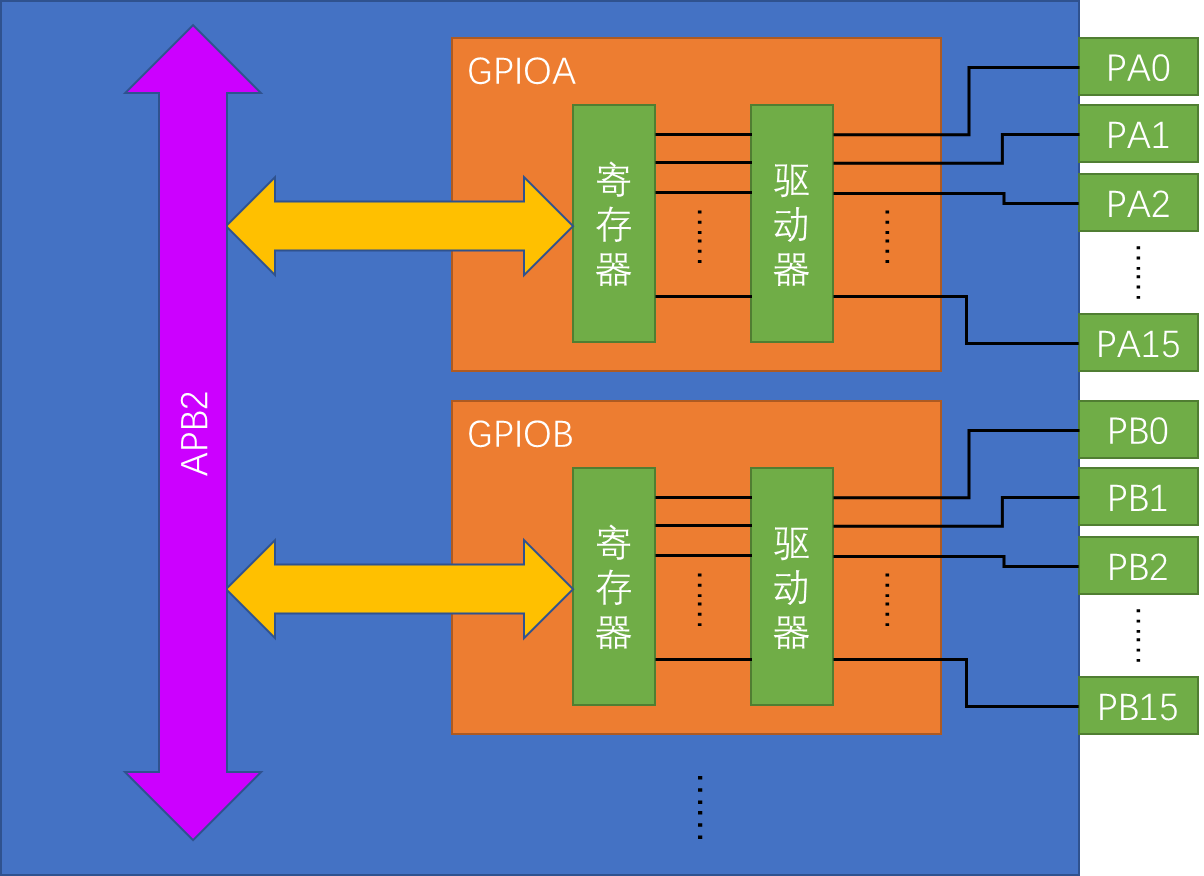

二、GPIO的基本结构

1、APB2 高速总线

最左边紫色的双向箭头,是 CPU 和 GPIO 外设之间的 “数据高速公路”。所有对 GPIO 的配置指令、数据读写,都要通过这条总线来传输。因为 APB2 是高速总线,所以 GPIO 这类需要快速响应的外设挂载在APB2 上。

2、GPIO 外设模块

中间的橙色块代表 GPIOA、GPIOB 这类独立的外设单元。每个模块都是一个完整的功能体,彼此独立工作,互不干扰。因此可以分别配置 PA0 和 PB0 。

3、寄存器与硬件驱动器

每个 GPIO 模块内部,分成了 “寄存器” 和 “硬件驱动器” 两个核心部分:

-

寄存器:是软件和硬件的 “翻译官”,我们通过修改寄存器的值来告诉硬件要做什么。比如配置引脚是输入还是输出,要输出高电平还是低电平。

-

硬件驱动器:负责把寄存器的数字指令,转化为引脚可以识别的电信号。它还内置了上拉 / 下拉电阻、开漏 / 推挽输出等硬件电路,决定了引脚的电气特性。

4、GPIO 引脚

最右侧的 PA0~PA15、PB0~PB15,就是芯片与外部世界连接的物理接口。我们最终就是通过这些引脚来控制 LED、读取按键状态,或者和其他设备通信的。

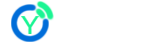

三、GPIO位结构

1、输入通路

-

模拟输入:信号直接进入片上外设(如 ADC),不经过数字触发电路,用于采集连续的模拟电压。

-

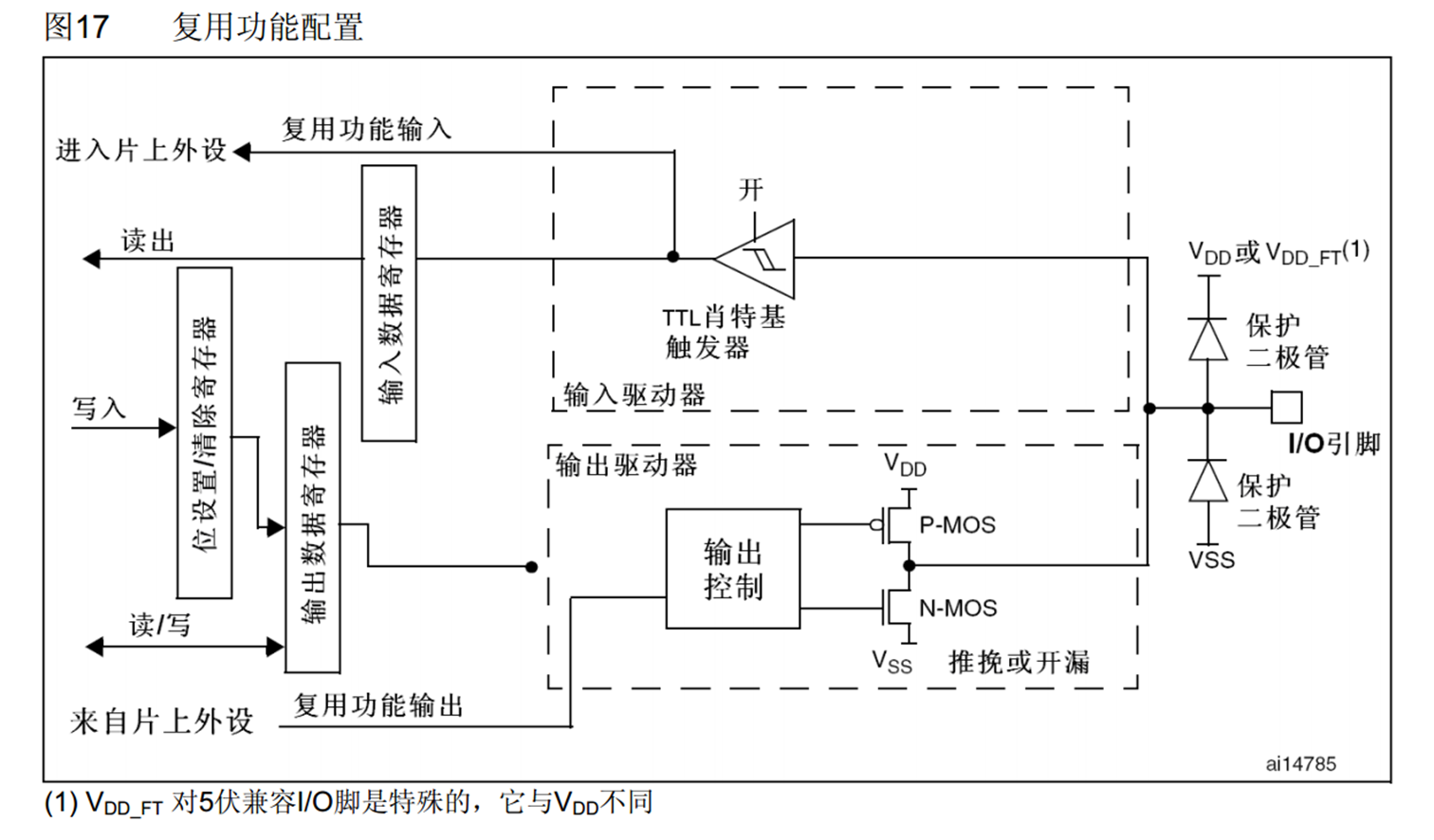

复用功能输入:信号会先经过 施密特触发器(TTL 肖特基触发器)进行电平整形,再传输到对应的片上外设(如 USART、SPI),用于接收数字通信信号。

-

通用输入:信号经触发器整形后存入输入数据寄存器,供 CPU 读取引脚的高低电平状态。

-

上拉 / 下拉电阻:通过开关可选择将引脚接 VDD(上拉)或 VSS(下拉),用于在引脚悬空时提供默认电平,避免信号不稳定。

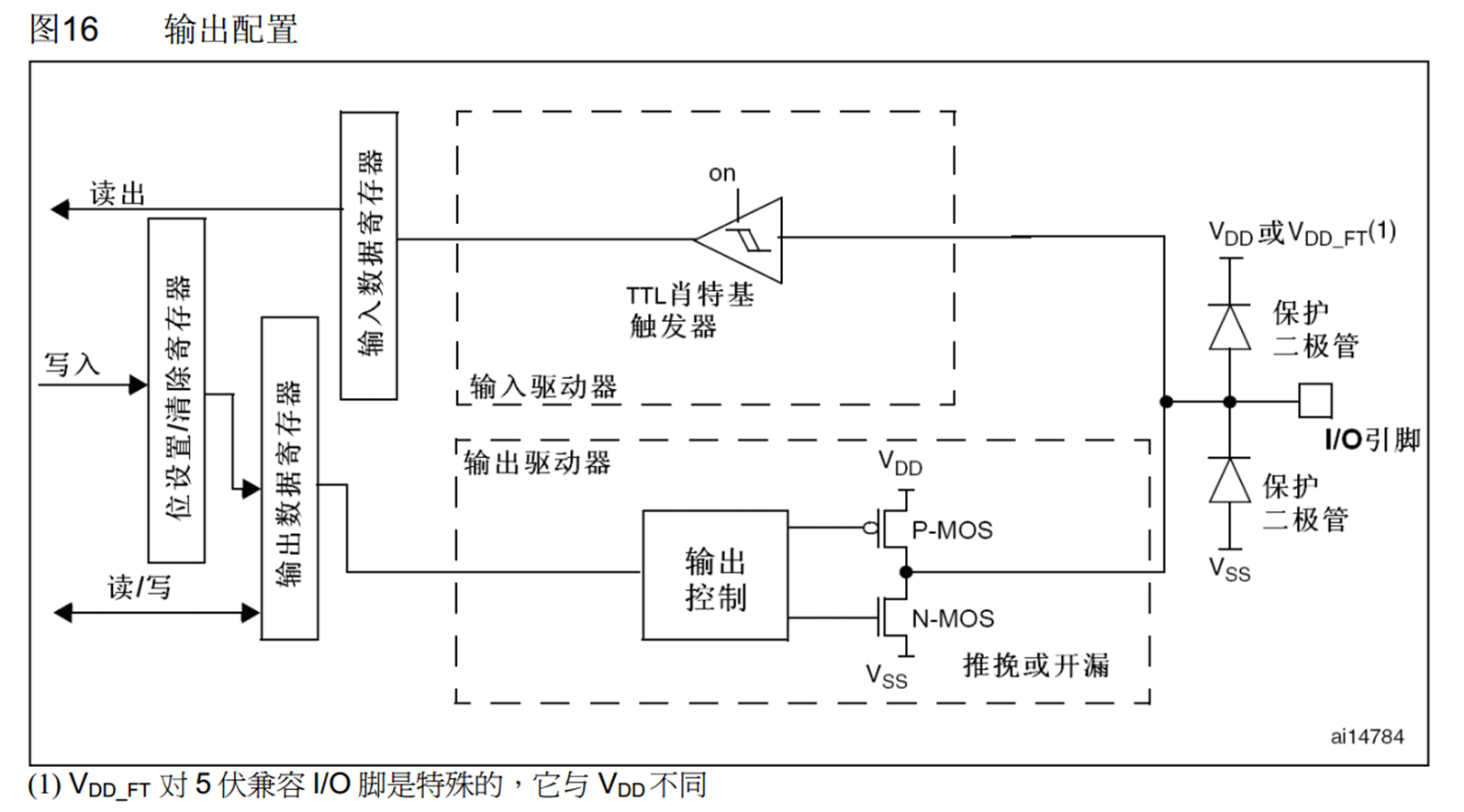

2、输出通路

-

输出控制与驱动器:核心由 P-MOS 和 N-MOS 管组成,可配置为三种模式:

-

推挽输出:P-MOS 和 N-MOS 协同工作,输出高电平时 P-MOS 导通、N-MOS 截止;输出低电平时则相反,驱动能力强,适合直接驱动 LED 等负载。

-

开漏输出:仅 N-MOS 工作,输出低电平时导通,输出高电平时呈高阻态,需要外部上拉电阻才能输出高电平,常用于 I²C 等需要线与逻辑的总线。

-

关闭状态:两个 MOS 管均截止,引脚处于高阻态,此时引脚仅可作为输入使用。

-

-

输出数据寄存器:存储 CPU 写入的输出电平指令,通过输出控制模块驱动 MOS 管动作。

-

复用功能输出:片上外设(如定时器 PWM、串口发送)的信号可直接通过输出驱动器从引脚送出,无需 CPU 干预。

3、 保护机制

引脚内置了两个反向并联的保护二极管:

-

当引脚电压高于 VDD时,上管导通,将多余电流导入 VDD。

-

当引脚电压低于 VSS时,下管导通,将多余电流导入 VSS。这可以防止静电、浪涌等异常电压损坏芯片内部电路。

4、寄存器交互

-

输出数据寄存器:CPU 通过 “写入” 或 “位设置 / 清除寄存器” 来更新输出电平。

-

输入数据寄存器:CPU 通过 “读出” 操作获取当前引脚的输入状态。

-

读 / 写接口:实现 CPU 对寄存器的访问,是软件控制硬件的核心通道。

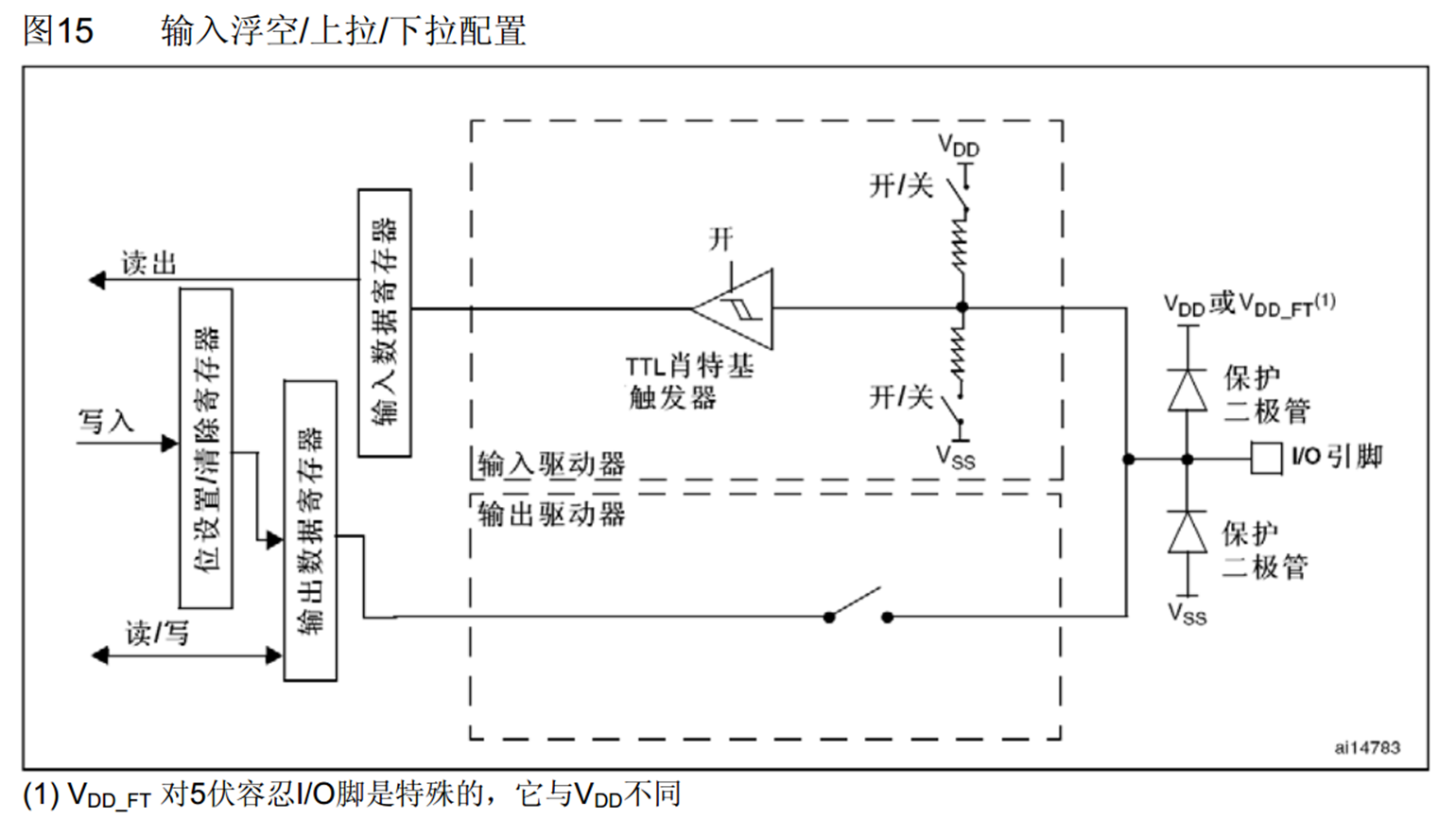

四、GPIO的输入模式

1、浮空输入

连接 VDD的上拉开关和连接 VSS的下拉开关均断开。引脚电平完全由外部信号决定,悬空时电平会受干扰而不稳定,仅适合连接确定的外部电平信号。

2、上拉输入

上拉开关闭合,下拉开关断开。内部上拉电阻将引脚默认电平拉至 VDD,当外部无输入时,引脚为高电平;当外部输入低电平时,引脚电平被拉低。

3、下拉输入

下拉开关闭合,上拉开关断开。内部下拉电阻将引脚默认电平拉至 VSS,当外部无输入时,引脚为低电平;当外部输入高电平时,引脚电平被拉高。

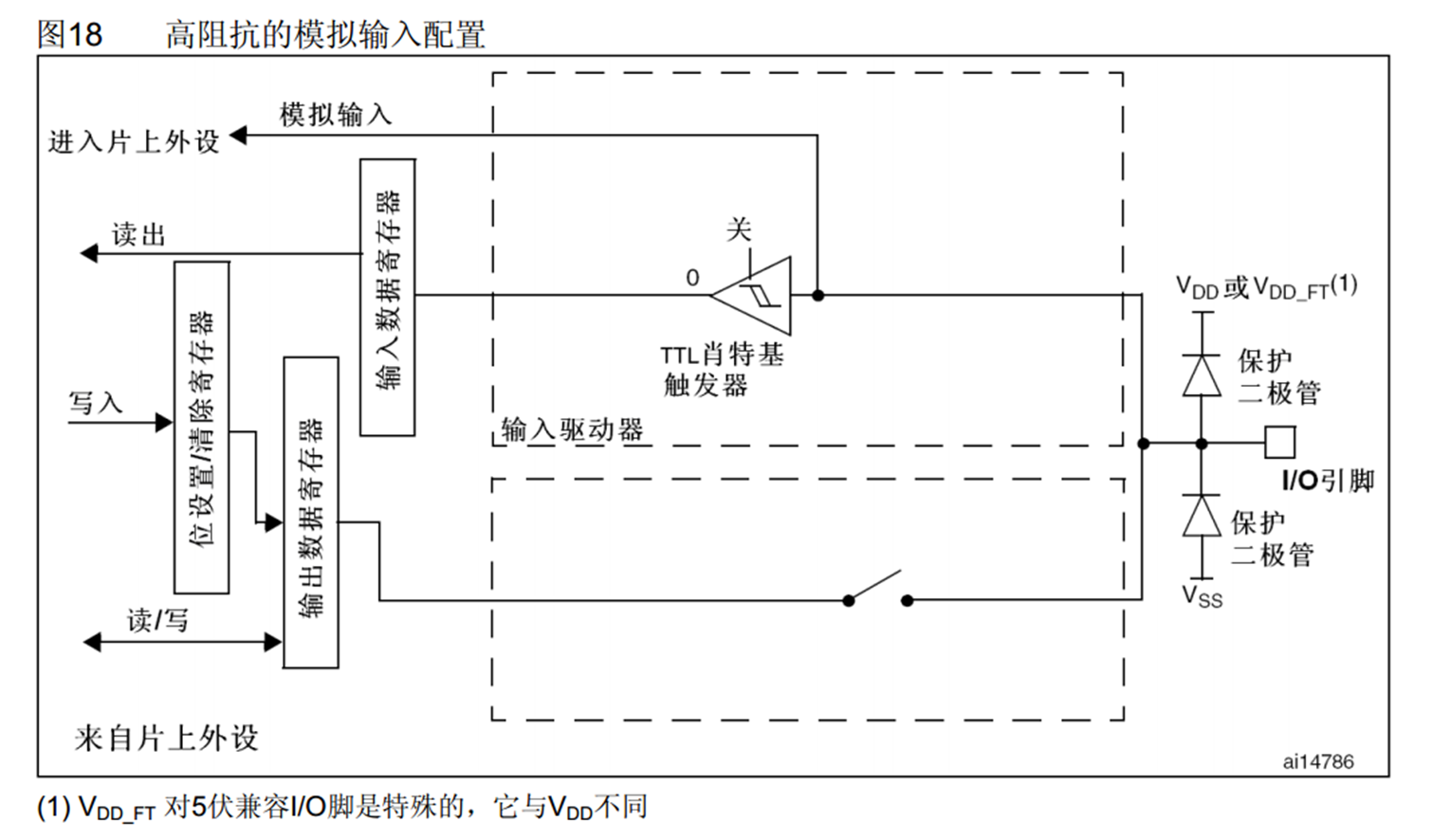

4、模拟输入

-

数字输入通路完全关闭:TTL 肖特基触发器处于 “关” 的状态,数字输入电路与引脚完全断开,避免数字电路的噪声干扰模拟信号。

-

信号直通片上外设:引脚的模拟信号不经过任何数字处理,直接通过 “模拟输入” 通路送入片上外设(如 ADC),最大程度保留了信号的原始波形。

图中的 VDD_FT 是针对 5V 容忍 I/O 引脚的特殊供电,它允许引脚直接输入 5V 电平而不损坏芯片,这部分 I/O 的上拉电阻由该电源供电,以保证 5V 信号的正确识别。

输出驱动器部分处于断开状态,确保输入模式下输出电路不会对输入信号产生干扰。

五、GPIO的输出模式

1、推挽输出

输出高电平时,P-MOS 导通、N-MOS 截止,引脚直接连接 VDD;输出低电平时,N-MOS 导通、P-MOS 截止,引脚直接连接 VSS。这种模式下驱动能力强,可直接驱动 LED、继电器等负载。

2、开漏输出

仅 N-MOS 管工作,输出低电平时 N-MOS 导通,引脚连接 VSS;输出高电平时两个管子均截止,引脚处于高阻态,需依赖外部上拉电阻才能输出高电平。

3、复用开漏输出

输出控制模块仅驱动 N-MOS 管,P-MOS 管始终处于截止状态。当外设输出低电平信号时,N-MOS 管导通,引脚被拉至 VSS(地)。当外设输出高电平信号时,N-MOS 管截止,引脚处于高阻态,必须依赖外部上拉电阻才能将电平拉至 VDD。

4、复用推挽输出

输出控制模块同时驱动 P-MOS 和 N-MOS 管,两者互补导通。当外设输出高电平信号时,P-MOS 管导通、N-MOS 管截止,引脚被拉至 VDD。当外设输出低电平信号时,N-MOS 管导通、P-MOS 管截止,引脚被拉至 VSS。

TTL 肖特基触发器处于 “开” 状态,保证输入信号的正确整形和传输。