ISP Pipeline 需要多次 DDR 读写以及一些行buffer缓冲原因

目录

一、先看基础事实:数据量极大

二、ISP 大量 DDR 读写的核心原因

1. 模块间解耦:不同单元吞吐 / 延迟不一致

2. 多帧复用:HDR、多帧降噪、EIS 必须读历史帧

3. 片上 SRAM 容量有限,只能 “分块处理”

4. 多路并发与异构输出:多路数据流分流

5. 格式转换与位深扩展:数据膨胀更占空间

6. 软件调试与回灌:需要可观测性

三、Buffer 缓冲的具体作用(为什么要这么多 Buffer)

四、为什么不能 “全链路直通、零 DDR”?

五、常见优化手段(工程上如何 “减少但无法消除” DDR)

1. 片上 SRAM 最大化

2. 数据压缩(Lossless/Low-loss)

3. 链路融合与旁路

4. 分块策略优化

5. QoS 与带宽调度

六、一句话总结

ISP Pipeline 之所以存在大量 DDR 读写与多级 Buffer,本质是为了解决 “实时图像处理” 与 “硬件并行架构” 之间的矛盾—— 图像数据量大、处理环节多、模块间吞吐不匹配,必须靠外部存储和缓冲来解耦、对齐、暂存、复用。下面从原理、必要性、典型场景、优化方向讲清楚。

一、先看基础事实:数据量极大

以常见 4K@30fps、10bit RAW 为例:

- 单帧 RAW:3840×2160×10bit ≈ 10MB / 帧

- 每秒流量:10MB×30 ≈ 300MB/s

ISP 流水线通常有 10~20 级处理单元,如果每级都 “直通不写回”,片上 SRAM 根本放不下,必须频繁进出 DDR。

二、ISP 大量 DDR 读写的核心原因

1. 模块间解耦:不同单元吞吐 / 延迟不一致

ISP 是多硬件加速器并行架构,每级处理能力不同:

- 有的模块快(如 Demosaic、CFA)

- 有的模块慢(如 3A 统计、TNR、HDR 合成、多帧融合)

如果不写 DDR 缓冲,快模块会被慢模块堵死,整链吞吐雪崩。DDR Buffer = 流量 “水库”,让上下游异步运行。

2. 多帧复用:HDR、多帧降噪、EIS 必须读历史帧

很多高级功能不是单帧处理,需要跨帧数据:

- HDR 多帧合成:长 / 中 / 短曝光帧对齐融合 → 多帧读写

- TNR 时域降噪:当前帧 + 历史多帧做运动估计 / 滤波 → 持续读写

- EIS 电子防抖:需要历史帧做特征跟踪、裁切补偿 → 读写历史帧

- 3A 统计:需要整帧统计结果回写、再分区域调度

这些功能天然依赖 DDR 暂存多帧。

3. 片上 SRAM 容量有限,只能 “分块处理”

ISP 硬件常用行缓冲 / 块处理模式:

- 片上 SRAM 一般只有 几百 KB~ 几 MB

- 无法存下一整帧 4K/8K 图像

- 只能读一块 → 处理 → 写回 DDR,循环直到整帧完成

分块必然带来多次 DDR 往返。

4. 多路并发与异构输出:多路数据流分流

现代 ISP 常同时输出多路:

- 预览流(Preview)

- 录像流(Video)

- 抓拍高分辨率流(Still)

- 3A 统计流、AI 检测流

不同分辨率、格式、帧率,必须在 DDR 中做分支与缓冲,否则硬件端口冲突。

5. 格式转换与位深扩展:数据膨胀更占空间

处理过程中数据会 “膨胀”:

- RAW 10bit → 线性 RGB 16/20bit → YUV 10bit

- 中间浮点 / 定点计算需要更高位宽防止溢出

中间结果更大,更难放在片上,只能写 DDR。

6. 软件调试与回灌:需要可观测性

工程上必须:

- 抓中间帧 Dump 定位问题

- 做回灌(Replay)复现 BUG

- 做效果调参、质量对比

这些都依赖中间节点写 DDR。

三、Buffer 缓冲的具体作用(为什么要这么多 Buffer)

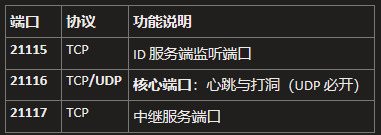

每一类 Buffer 对应一类工程约束,常见分类:

| Buffer 类型 | 作用 | 典型位置 |

|---|---|---|

| 输入帧缓冲 | 接收 MIPI 接收的 RAW,给 ISP 异步读取 | MIPI RX 后 |

| 行缓冲 / 块缓冲 | 支持卷积、滤波、插值的局部邻域访问 | 片上,Demosaic、Sharpening 等 |

| 跨帧缓冲 | 存储历史帧用于 TNR、HDR、EIS | DDR,多帧模块前后 |

| 分支缓冲 | 分流 Preview/Video/Still 等不同路径 | 多路输出前 |

| 统计缓冲 | 存放 AE/AWB/AF 统计直方图 / 网格 | 统计单元后 |

| 回灌缓冲 | 保存中间结果用于调试与质量回归 | 关键节点(LSC、Bayer、YUV 等) |

| 旋转 / 裁切缓冲 | 做 90/270° 旋转、畸变校正、ROI 裁切 | 输出前 |

多级 Buffer = 流水线 “寄存器重命名 + 流量整形”,保证并行、无死锁、低抖动。

四、为什么不能 “全链路直通、零 DDR”?

理论上可以做极短流水线、小分辨率、单功能直通,但实际产品做不到:

- 分辨率越来越大(8K/16K),片上存不下

- 功能越来越多(HDR、TNR、EIS、DOL、SMIA 多帧)必须跨帧

- 多路并发输出必须缓冲分支

- 时序收敛要求模块间解耦,否则 PVT 波动会导致丢帧

- 调试与量产质量需要中间可观测

零 DDR 只适合极简监控 / 低分辨率传感器,手机 / 汽车 / 安防都不可能。

五、常见优化手段(工程上如何 “减少但无法消除” DDR)

1. 片上 SRAM 最大化

- 增大行缓冲、块缓冲

- 做数据重排 / 打包,减少读写粒度浪费

2. 数据压缩(Lossless/Low-loss)

- 在线压缩 RAW/YUV

- 减少 DDR 有效带宽,典型可降 30%~60%

3. 链路融合与旁路

- 能 “串起来不写回” 的模块尽量合并

- 非调试场景关闭中间节点 Dump

- 动态旁路不需要的功能(如低光关闭强锐化)

4. 分块策略优化

- 更大块处理,减少读写次数

- 预取 / 写合并,提高总线效率

5. QoS 与带宽调度

- 给 ISP 高优先级,减少 DDR 等待延迟

- 与 CPU/GPU/Display 做带宽隔离

六、一句话总结

ISP Pipeline 大量 DDR 读写与多级 Buffer,是 “大分辨率 + 多帧算法 + 多硬件并行 + 片上资源有限 + 多路输出” 共同决定的,是性能、实时性、功能、可调试性之间的必然折中。它不是 “浪费”,而是现代 ISP 能跑起来的基础架构。